CS 5620/6620 - Fall 2025 - Rendering with Ray Tracing

Project 8 - Antialiasing

Zhuoran Yi

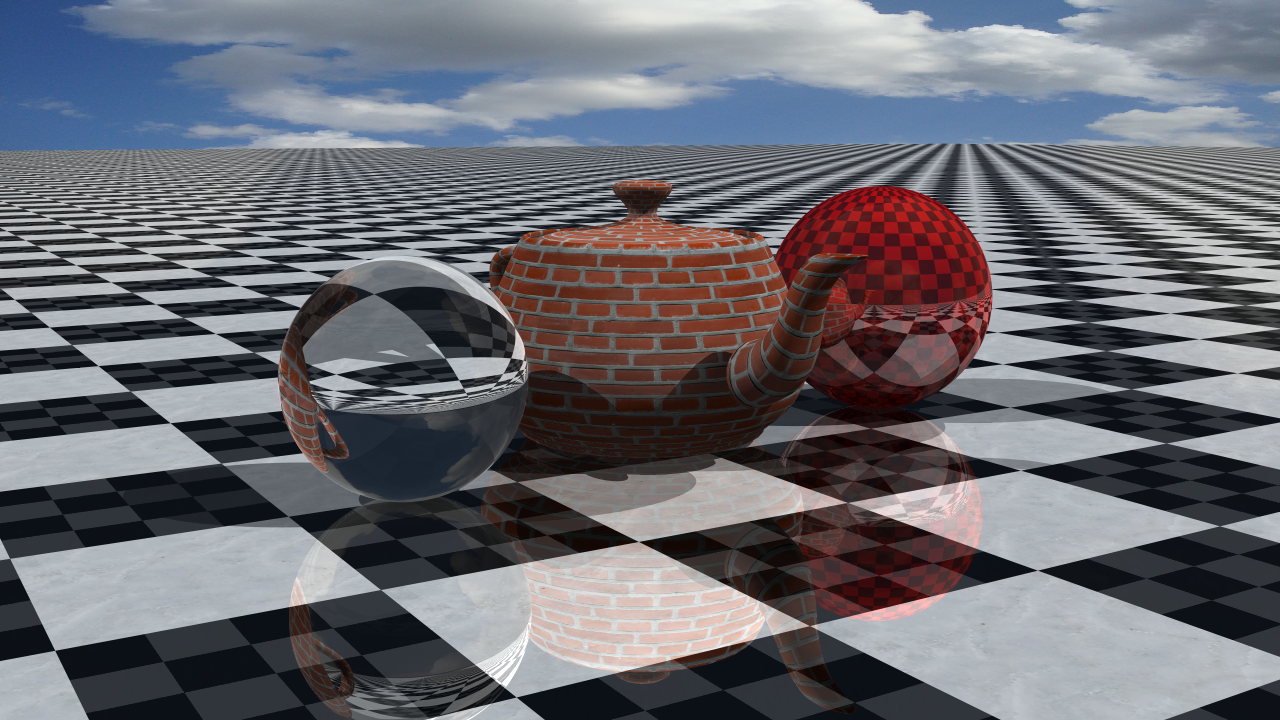

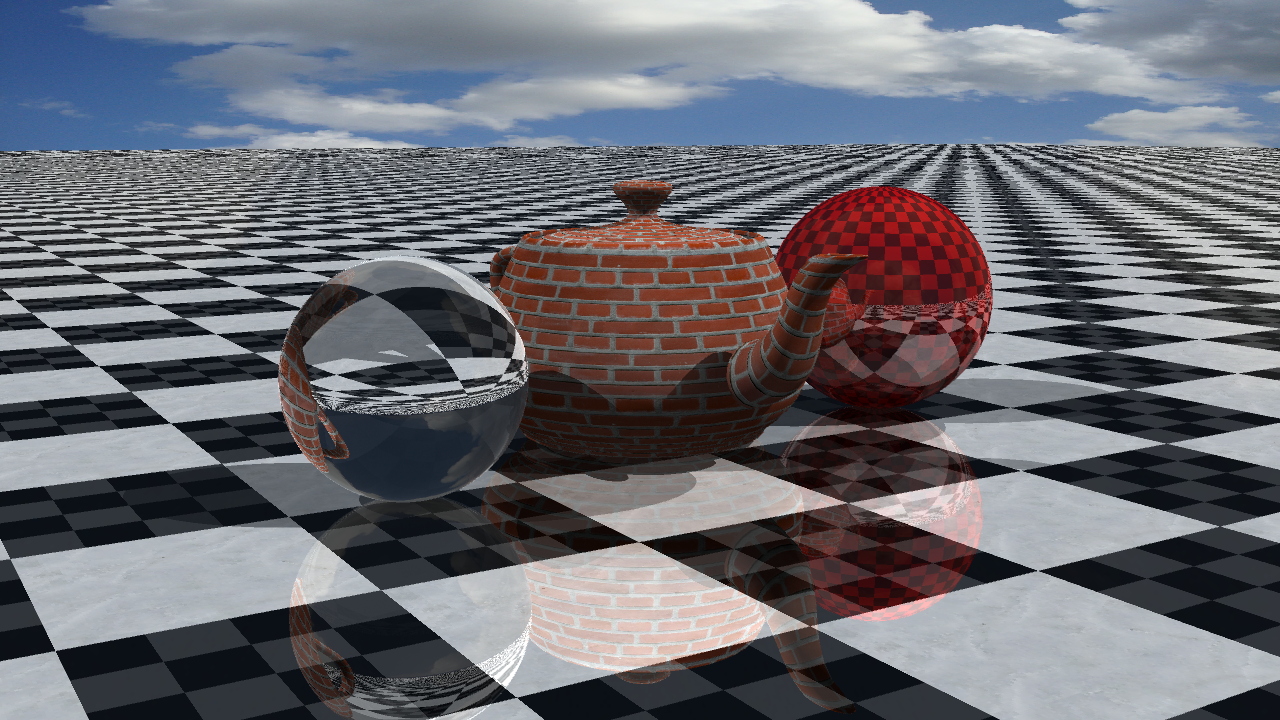

2D Halton, SPP min = 4, SPP max = 256, Tile Size 8x8, variance threshold = 0.01, confidence = 95%, Intel Core Ultra9 285H 6P+8E Cores, 47seconds, As AWS causes an major outage of Canvas, I have to submit the code with a slightly delay.

2D Halton, SPP min = 4, SPP max = 256, Tile Size 8x8, variance threshold = 0.01, confidence = 95%, Intel Core Ultra9 285H 6P+8E Cores, 47seconds

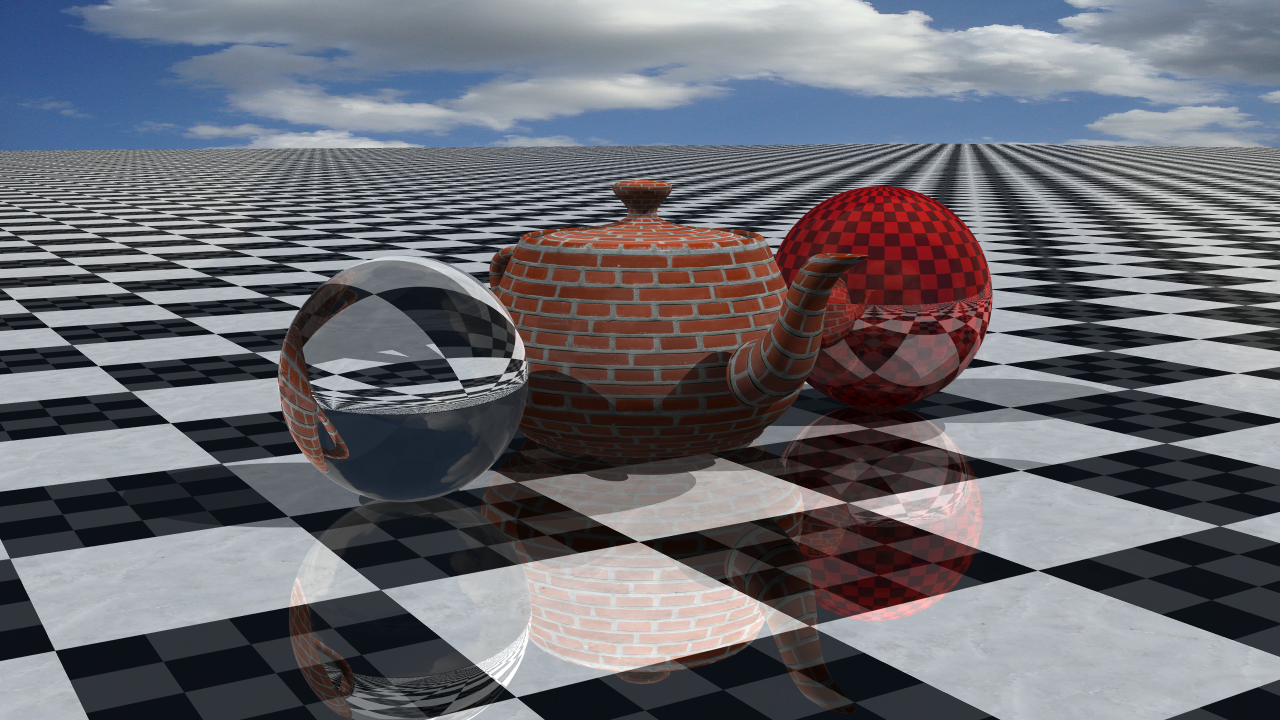

2D Halton, SPP min = 4, SPP max = 16, Tile Size 1x1, variance threshold = 0.01, Intel Core Ultra9 285H 6P+8E Cores, 20minutes. As the tile size is 1x1, the edge of each tile is clear.

2D Halton, SPP min = 4, SPP max = 16, Tile Size 1x1, variance threshold = 0.01, Intel Core Ultra9 285H 6P+8E Cores, 20minutes.

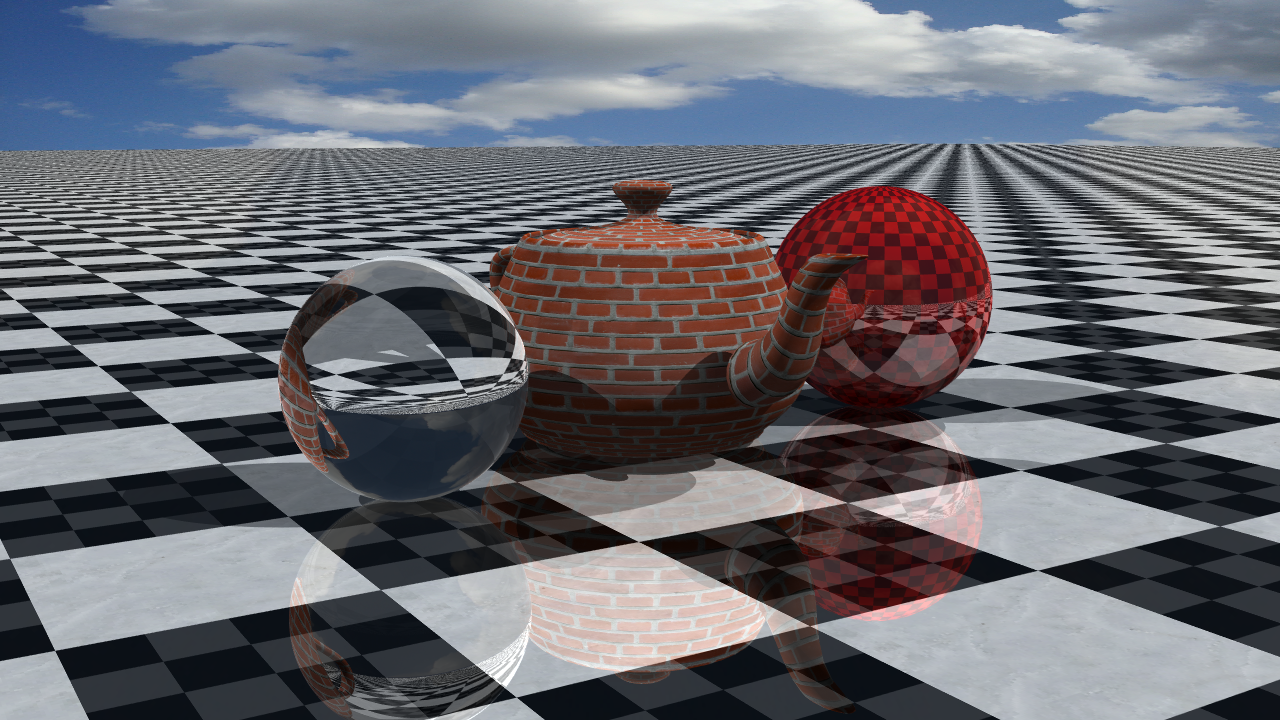

2D Halton, SPP min = 4, SPP max = 256, Tile Size 8x8, variance threshold = 0.01, Intel Core Ultra9 285H 6P+8E Cores, 33seconds. As I used Tile Based Rendering with consistent threads, the edge of each tile is clear.

2D Halton, SPP min = 4, SPP max = 256, Tile Size 8x8, variance threshold = 0.01, Intel Core Ultra9 285H 6P+8E Cores, 33seconds

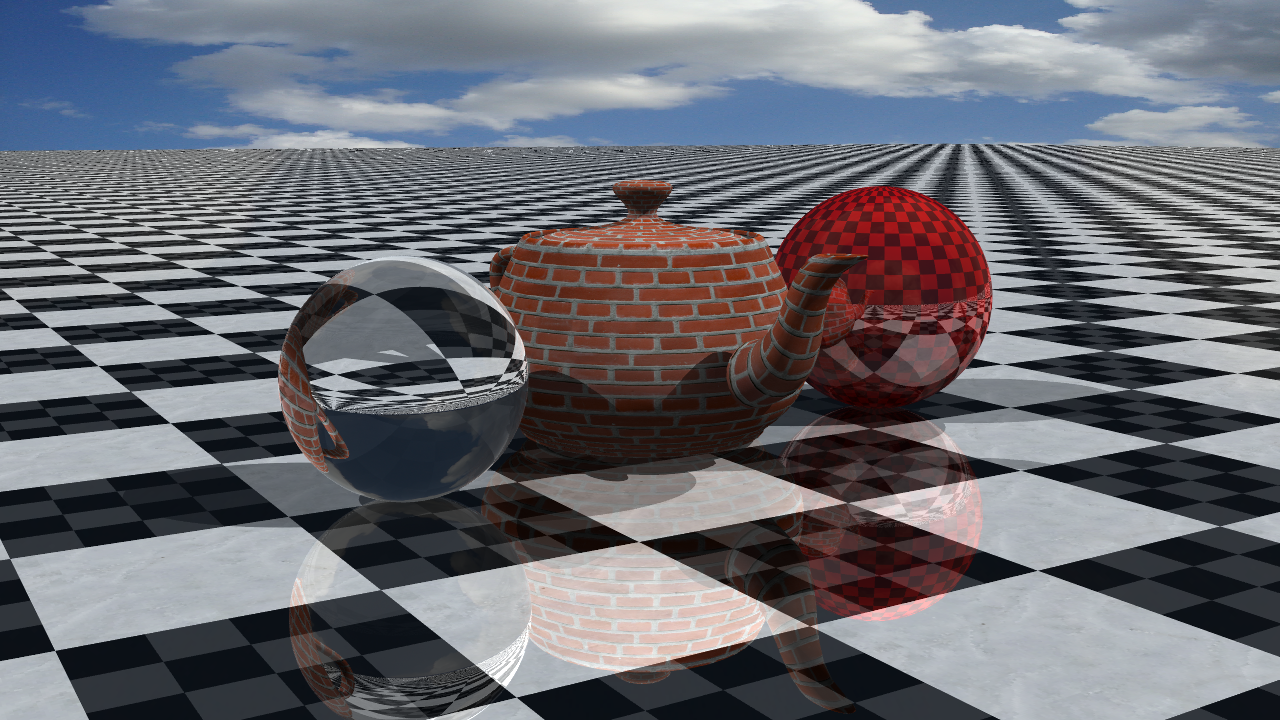

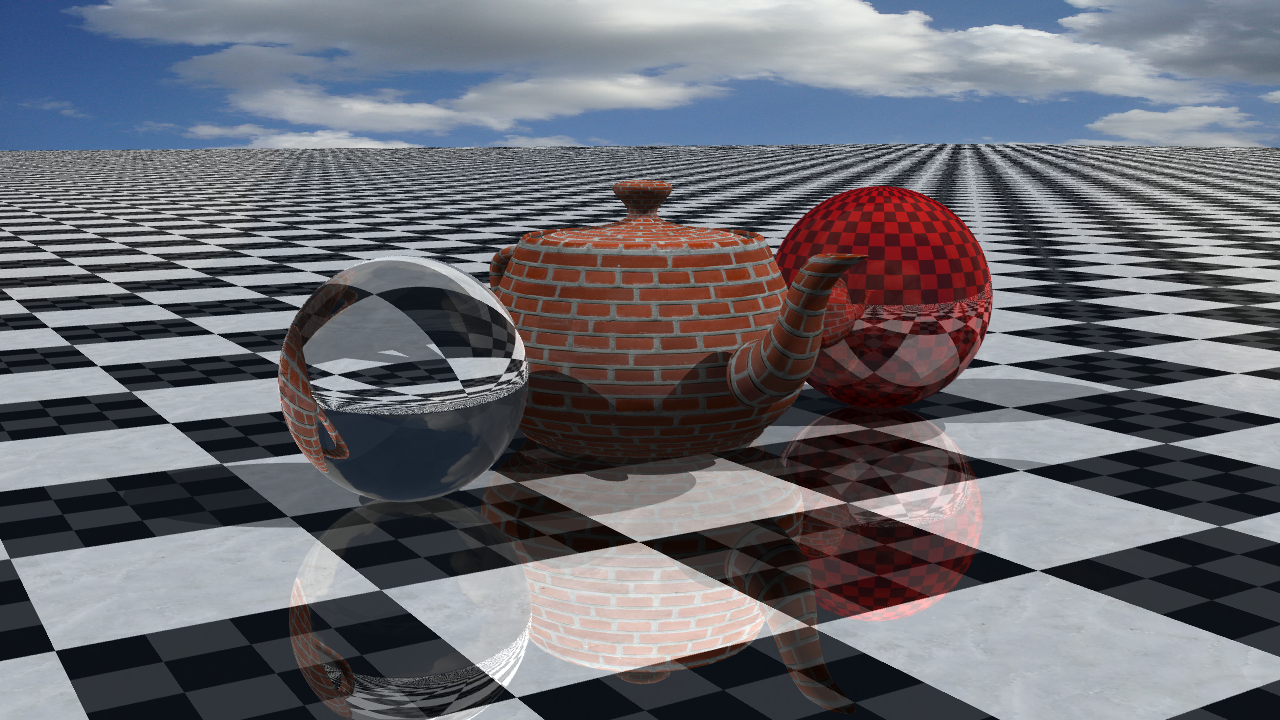

2D Hammersley, SPP = 16.

2D Hammersley, SPP = 8

2D Hammersley, SPP = 4

2D Hammersley, SPP = 2